Čínský gigant Taiwan Semiconductor Manufacturing Co. (TSMC) přijde někdy kolem letošních prázdnin s novou technologií čipů. Tyto čipy by měli mít hustotu tranzistorů až 1000x větší než dosavadní vyráběné čipy. V tomto případě se jedná o nejvýznamější změnu od padesátých let 20. století, co se čipů týče. TSMC tak chtějí soupeřit s firmou Intel který na začátku roku oznámil podobnou technologii 3D čipů s názvem Tri-Gate. Tyto čipy Tri-Gate by měly podle všeho sloužit zejména v oblasti zařízení jako jsou smartphony a touchpady. Tento typ čipů obsahuje několik vrstev křemíku, a tím se zvýšuje výkon čipu o 1/3 a příkon se sníží až o 50 procent, což se pro mobilní zařízení dokonale hodí.

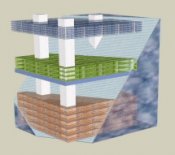

Zde můžeme vidět jednotlivé Vrstvy 3D čipu - propoje, paměť a mikroporcesor (shora dolů).

Od těchto nových křemíkových integrovaných obvodech se očekává veliká úleva od řešení problémů s nárůstem teploty při stálem zmenšování technologie. Tyto problémy způsobují zpoždění signálu, tedy omezují rychlost hodin, které se nachází v každé centrální procesorové jednotce a generují signál (oscilátor).

"3D čipy jsou atraktivnější kvůli větší hustotě tranzistorů. Nicméně, je obtížnější jejich výroba, protože když máme 5 vrstev a jedna z nich je vadná, celý čip je nepoužitelný.", řekl, Shang-Yi Chiang, více president pro výzkum a vývoj v TSMC. Z tohoto důvodu, TSMC také rozvíjí tzv. 2D čipy, které nahradí organický polymer, což je substrát křemíku sloužící pro zvýšení hustoty tranzistorů.

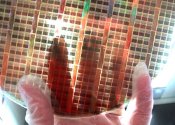

Takto vypadá matice již vyrobených polovodičových čipů:

Xilinx vyrábí optimalizované čipy rodiny Virtex s vysokým výkonem a nizkým příkonem, které slouží zejména pro komunikační hardware (např. letecký a dopravní systém). Pro výrobu třetího člena Virtex-7 FPGA, Xilinx uzavřel dohodu s TSMC, protože Virtex-7 FPGA bude využívat tuto technologii, kde budou umístěny na sobě tři křemíkové destičky na jednom substrátě. První produkty by se tak měli podle všeho objevit už během letošního srpna.

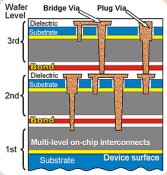

První 3D čipy byli představeny firmou IBM a organizacemi Defense Advanced Research Project Agency (DARPA) a Rensselaer Polytechnic Institute (RPI) už v roce 2007, kde bylo několik vrstev křemíku propojeno technikou označovanou jako wafer bonding (spojování waferů). Tato metoda spojuje vrstvy křemíku pomocí vertikálních "stopek", které prochází přes další spodní vrstvu a tím je zařízen propoj miezi jednotlivými vrstvami (viz. obrázek níže).

Větší hustota tranzistorů způsobuje také menší vzdálenost mezi nimi, a tak data cestují menší vzdálenost. Výsledkem je mnohonásobně rychlejší zpracovávání dat.

2024 ©

2024 ©